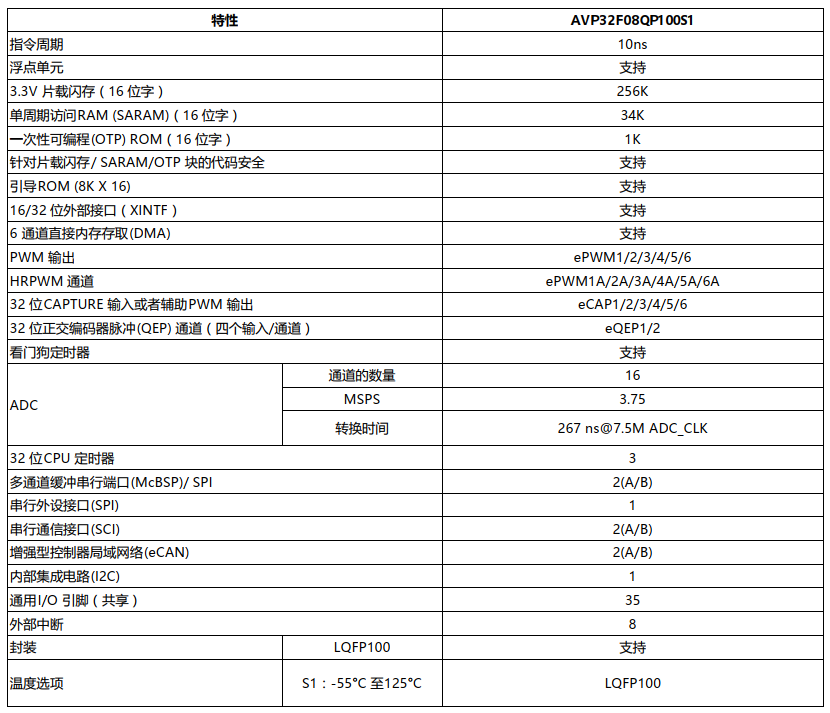

AVP32F08是根据LQFP100引脚资源,特殊定义的一款高性能DSP,芯片内部采用AVP32F335相同的芯片设计。

AVP32F08(CPU+FPU)系列都属于ADP32Fx数字信号控制器(DSP)平台。基于ADP32x+FPU的控制器和Advchip现有的ADP32FxDSP具有相同的32位定点架构,但是还包括一个单精度(32位)的IEEE754浮点单元(FPU)。这是一个非常高效的C/C++引擎,它能使用户用高层次的语言开发他们的系统控制软件,能够使用C/C++开发算术算法。此器件同样可以处理原由微控制器处理的系统控制任务,故在处理DSP算术任务时和处理系统控制任务时同样有效。此高效率处理可以节省很多系统对对第二个处理器的需求。内置的32x32位MAC64位处理能力使得控制器能够有效地处理更高的数字分辨率运算问题。带有关键寄存器自动环境保存的快速中断响应,能够让一个器件用最小的延迟处理很多异步事件。还内置有一个具有流水线式存储器访问的8级深度受保护的流水线。该流水线式操作使得此器件能够在高速执行而无需求助于昂贵的高速存储器。特别分支超前硬件大大减少了条件不连续而带来的延迟。特别存储条件操作进一步提升了性能。

|

● 高性能静态CMOS技术 |

○ 高达6个事件捕捉输入 |

|

○ 高达100MHz(10ns周期时间) |

○ 多达2个正交编码器接口 |

|

○ 1.8V转1.5V内核,3.3V I/O设计 |

○ 8个32位定时器(6个eCAP,2个eQEP) |

|

● 高性能32位CPU |

○ 9个16位定时器(6个ePWM,3个XINTCTR) |

|

○ IEEE-754单精度浮点单元(FPU) |

● 三个32位CPU定时器 |

|

○ 16 x 16和32 x 32乘加运算(MAC) |

● 串行端口外设 |

|

○ 16 x 16双乘加 |

○ 2个控制器局域网(CAN)模块 |

|

○ 哈佛(Harvard)总线架构 |

○ 2个SCI (UART)模块 |

|

○ 快速中断响应和处理 |

○ 2个McBSP模块(McBSP-A/B可配置为SPI) |

|

○ 统一存储器编程模型 |

○ 1个SPI模块 |

|

● 6通道DMA处理器(用于ADC,McBSP,ePWM,XINTF和SARAM) |

○ 1个内部集成电路(I2C)总线 |

|

● 片载存储器 |

l12位模数转换器(ADC),16个通道 |

|

○ 256K×16闪存,34K×16 SARAM |

○ 12位—(267ns转换时间@7.5MHz ADC_CLK) |

|

○ 1K x 16一次性可编程(OTP) ROM |

○ 16个通道(2 x 8输入复用) |

|

● 引导ROM (8K X 16) |

○ 2个采样保持 |

|

○ 支持软件引导模式(通过SCI,SPI,CAN,I2C,McBSP,XINTF和并行I/O) |

○ 顺序/并发转换模式 |

|

○ 标准数学表 |

○ 内部或者外部基准 |

|

● 时钟和系统控制 |

● 35路复用(GPIO)引脚 |

|

○ 支持动态锁相环(PLL)比率变化 |

● JTAG边界扫描支持 |

|

○ 片载振荡器 |

● 高级仿真特性 |

|

○ 看门狗定时器模块 |

○ 分析和断点功能 |

|

● GPIO0到GPIO34引脚可以连接到八个外部内核中断其中的一个 |

○ 硬件实时调试 |

|

● 可支持全部58个外设中断的外设中断扩展(PIE)块 |

● 开发支持 |

|

● 128位安全密钥/锁 |

○ ANSI C/C++编译器/汇编语言/连接器 |

|

○ 保护闪存/ OTP/RAM模块 |

○ Code Composer Studio |

|

○ 防止固件逆向工程 |

○ 数字电机控制和数字电源软件库 |

|

● 低功耗模式和省电模式 |

● ESD:2000V |

|

○ 支持IDLE、STANDBY、HALT模式 |

● 封装选项 |

|

● 字节序:小端序 |

○ LQFP100 |

|

○ 多达16个脉宽调制(PWM)输出 |

● 温度选项 |

|

○ 高达6个支持150ps微边界定位(MEP)分辨率的 |

○ S1:-55°C至125°(筛选) |

|

● 高分辨率脉宽调制器(HRPWM)输出 |

|

版权所有:Copyright@2021 星空体育(中国)官方网站 地址:长沙市湘江新区东方红街道北斗产业园·黄金园A5栋 营业执照查阅 湘ICP备18010582号-1 网站地图

技术支持:竞网智赢